Efabless has launched a 100% open-source FPGA chip CLEAR, built on Caravel – an open-source ASIC platform provided as a base (SoC) and offering an end-to-end open design, right down to the CPU core. The explanation of the product is simple and quite relatable to the maker’s community – “create your own ASIC.”

The process started in 2020 when eFabless, Google and SkyWater collaborated to offer the Open MPW Shuttle Program. It offered the end-users ability to create custom ICs fast, using pre-verified blocks of EFabless IP. As part of the Open MPW Shuttle Program, EFabLess exposes pre-verified blocks of IP through a web portal for complete ASIC design, with drag-and-drop features.

SkyWater pools design together into real-life ASICs – manufacturing, bonding, and packaging 10 parts of each design, ready for integration by the end-user. Apart from this, Google sponsored additional tooling costs. All this is for open-source designs that can meet the Open MPW Shuttle program’s requirements. It basically enables ASIC customization in the drag-and-drop web environment, with 10 copies produced on an industrial process, free of cost.

The pre-validated IP provided by EFabLess for custom ASIC creation is Caravel. It is a reference design block for the SkyWater process, and massively bootstraps the design process for any new chip. An extension to the Open MPW Shuttle Program is the EFabless chipIgnite Program. Where the Open MPW Shuttle Program required submissions to be properly licensed to open hardware, chipIgnite is open to all for a one-off $9,750 per project.

CLEAR is an enhancement on EFabless chipIgnite platform, itself an expansion of the Open MPW Shuttle Program for producing custom ASIC. It integrates an embedded FPGA macro with Caravel to make it an FPGA ASIC, or simply programmable application-specific IC.

Features of CLEAR

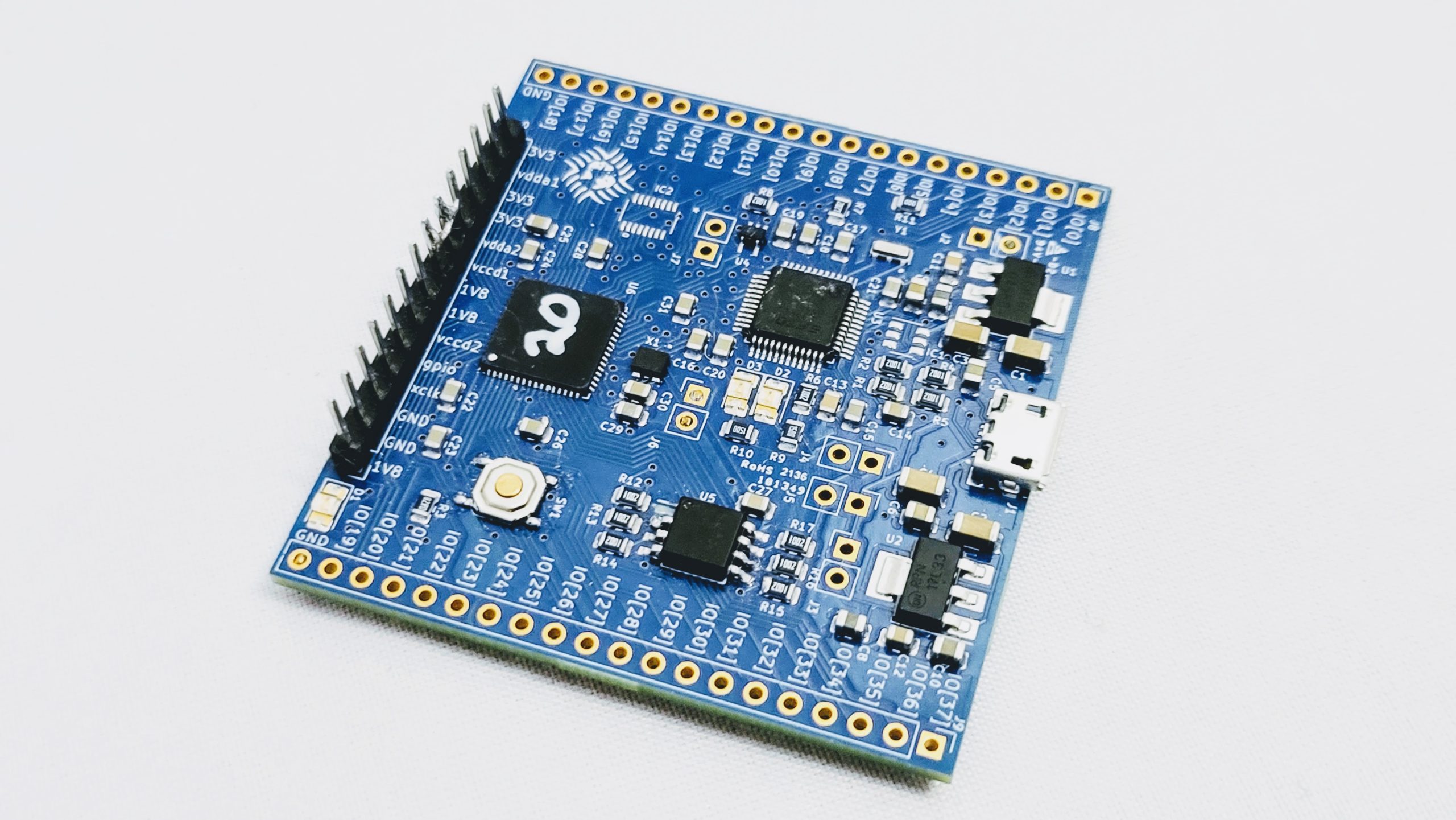

Some of the features of the CLEAR board include full open-source ASIC featuring an 8×8 CLB embedded FPGA (eFPGA), VexRISCV-based RISC-V processor, 3kB of on-chip RAM(2kB OpenRAM and 1kB DFFRAM), external QSPI flash storage, and peripherals including SPI, UART, counters, timers, a logic analyzer, and 39 software-configurable general-purpose input/output (GPIO) pins.

The idea behind CLEAR is to simplify, standardize and bring down costs of ASIC design.

GroupGets Pre Launch Campaign

Running through the GroupGets group-buying platform the CLEAR campaign includes:

- Generate an embedded FPGA macro based on OpenFPGA generator framework

- Integrate the eFPGA macro into Caravel

- Manufacturing, packaging and mounting the ASIC on its development board

- Testing plus the open-source FPGA programming software

GroupGets has started a pre-launch campaign, with pricing of $74.99 plus shipping. 200 boards target. The funding campaign is currently active and scheduled to end on March 28th, 2022.

To know more about the product, please visit the groupgets page.

![W88 [Rủi Ro Khi Chơi Nổ Hũ: Lưu Ý Quan Trọng Nhất Cho Người Chơi]](https://theskil.com/wp-content/themes/rehub-theme/images/default/noimage_336_220.png)